# SYN6988语音合成芯片 硬件数据手册

# 北京宇音天下科技有限公司

宇音天下官方订阅号

|     | SYN6988 语音合成芯片硬件数据手册修正记录 |        |  |  |  |

|-----|--------------------------|--------|--|--|--|

| 版本  | 版本 发布日期 内容描述             |        |  |  |  |

| 1.0 | 2021/04/12               | 首次发布版本 |  |  |  |

|     |                          |        |  |  |  |

# 重要声明

### 版权声明

版权归北京宇音天下科技有限公司所有,保留所有权利。

### 商标声明

北京宇音天下科技有限公司的产品是北京宇音天下科技有限公司专有。在提及其他公司及其产品时将使用各自公司所拥有的商标,这种使用的目的仅限于引用。本文档可能涉及北京宇音天下科技有限公司的专利(或正在申请的专利)、商标、版权或其他知识产权,除非得到北京宇音天下科技有限公司的明确书面许可协议,本文档不授予使用这些专利(或正在申请的专利)、商标、版权或其他知识产权的任何许可协议。

### 不作保证声明

北京宇音天下科技有限公司不对此文档中的任何内容作任何明示或暗示的 陈述或保证,而且不对特定目的的适销性及适用性或者任何间接、特殊或连带的 损失承担任何责任。本手册内容若有变动,恕不另行通知。本手册例子中所用的 公司、人名和数据若非特别声明,均属虚构。未得到北京宇音天下科技有限公司 明确的书面许可,不得为任何目的、以任何形式或手段(电子的或机械的)复制 或传播手册的任何部分。

### <u>保密声明</u>

本文档(包括任何附件)包含的信息是保密信息。接收人了解其获得的本文 档是保密的,除用于规定的目的外不得用于任何目的,也不得将本文档泄露给任 何第三方。

本软件产品受最终用户许可协议(EULA)中所述条款和条件的约束,该协议位于产品文档和/或软件产品的联机文档中,使用本产品,表明您已阅读并接受了EULA的条款。

版权所有: 北京宇音天下科技有限公司

# 目录

| 1. |                              |    |

|----|------------------------------|----|

|    | 1.1 SYN6988 的 LQFP-64L 的封装图片 | 5  |

|    | 1.2 SYN6988 的引脚视图            | 6  |

|    | 1.3 SYN6988 的引脚定义            | 7  |

| 2  | SYN6988 的参考电路                | 8  |

|    | 2.1 免责声明                     | 8  |

|    | 2.2 典型应用电路                   | 9  |

|    | 2.3 复位方式                     |    |

|    | 2.3.1 芯片复位外部条件               |    |

|    | 2.3.2 芯片初始化输出                | 10 |

|    | 2.4 复位电路选择                   | 11 |

|    | 2.5 与上位机通讯连接                 |    |

|    | 2.5.1 UART 通讯                |    |

|    | 2. 5. 2 SPI 通讯               | 14 |

|    | 2.6 音频功放电路                   | 14 |

|    | 2.7 电源电路                     |    |

|    | 2.7.1 PowerIN                |    |

|    | 2.7.2 VREF (PIN18)           |    |

|    | 2.7.3 PLL_V12 (PIN24)        | 16 |

|    | 2.7.4 VDD3_0 (PIN38)         |    |

|    | 2.7.5 VDD2_0 (PIN23)         | 16 |

|    | 2.7.6 VDDIO1_0 (PIN22)       | 16 |

|    | 2.8 外接高速晶振                   |    |

|    | 2.9 评估模块电路原理图                |    |

|    | 2.10 Readby/Busy 接口电压跟随器电路   |    |

| 3  | 制板注意事项                       |    |

|    | 3.1 晶振布局                     |    |

|    | 3.2 电容布局                     |    |

|    | 3.3 音频线布线                    |    |

|    | 3.4 DCDC 电源电路                | 20 |

| 4  | SYN6988 产品规格                 | 20 |

|    | 4.1 SYN6988 的封装数据图           | 20 |

|    | 4.2 电气特性                     | 21 |

|    | 4.2.1 极限参数                   | 21 |

|    | 4.2.2 推荐电压工作范围               |    |

|    | 4. 2. 3 音频 DAC 特性            |    |

|    | 4. 2. 4 DC 电气特性              | 22 |

|    | 4.3 播放合成声音时的功耗               |    |

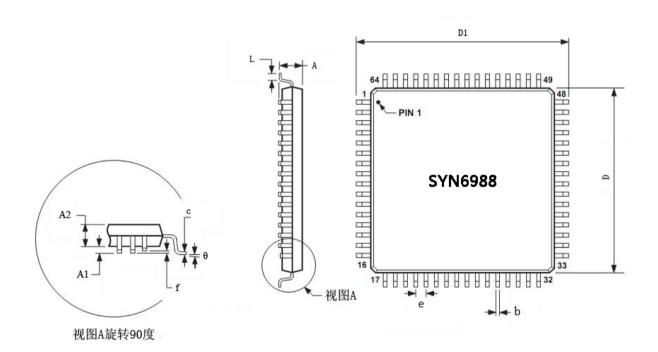

- 1. SYN6988 的封装信息

- 1.1 SYN6988 的 LQFP-64L 的封装图片

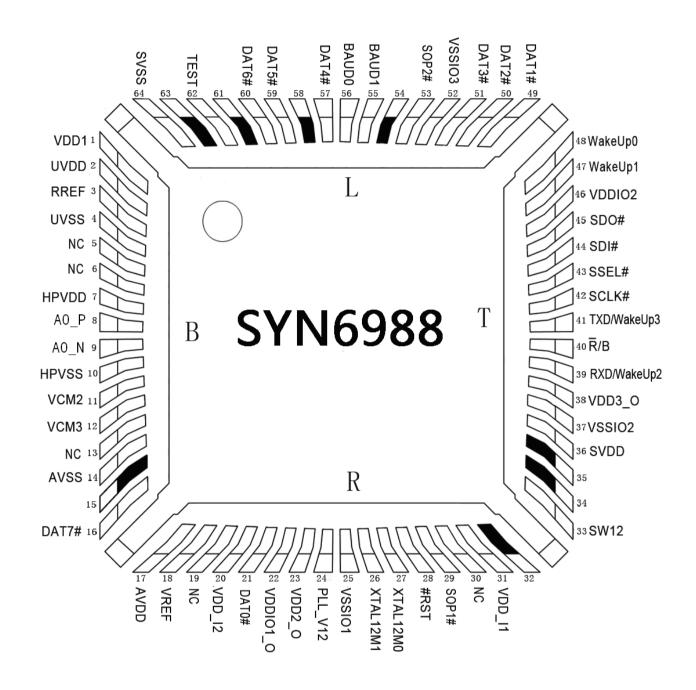

# 1.2 SYN6988 的引脚视图

# 1.3 SYN6988 的引脚定义

| 编号 | 引脚       | 说明                                                             | 编号 | 引脚              | 说明                             |

|----|----------|----------------------------------------------------------------|----|-----------------|--------------------------------|

| 1  | VDD1     | 1.2V 数字电源输入                                                    | 33 | SW12            | 外面须接一 10uH 电感和一<br>肖特基二极管      |

| 2  | UVDD     | 3. 3V 模拟电源输入                                                   | 34 |                 | Undefined                      |

| 3  | RREF     | 参考电压,10K 下拉电阻                                                  | 35 |                 | Undefined                      |

| 4  | UVSS     | 数字地                                                            | 36 | SVDD            | 3. 3V 数字电源输入                   |

| 5  | NC       |                                                                | 37 | VSSI02          | 数字地                            |

| 6  | NC       |                                                                | 38 | VDD3_0          | 1.2V 数字电源输出                    |

| 7  | HPVDD    | 3. 3V 模拟电源输入                                                   | 39 | RXD/WakeU<br>P2 | 串口接收/WakeUP2<br>不用时外接 10k 上拉电阻 |

| 8  | A0_P     | 音频输出-正                                                         | 40 | R/B             | 芯片忙状态指示, 低电平表<br>示空闲           |

| 9  | AO_N     | 音频输出-负                                                         | 41 | TXD/WakeU<br>P3 | 串口发送/WakeUP3                   |

| 10 | HPVSS    | 模拟地                                                            | 42 | SCLK#           | SPI_SCLK                       |

| 11 | VCM2     | 外接 10uF 滤波电容                                                   | 43 | SSEL#           | SPI_SSEL                       |

| 12 | VCM3     | 外接 10uF 滤波电容                                                   | 44 | SDI#            | SPI_MOSI                       |

| 13 | NC       |                                                                | 45 | SDO#            | SPI_MISO                       |

| 14 | AVSS     | 模拟地                                                            | 46 | VDDIO2          | 3. 3V 数字电源输入                   |

| 15 |          | Undefined                                                      | 47 | WakeUp1         | 唤醒引脚1                          |

| 16 | DAT7#    | 数字信号线                                                          | 48 | WakeUp0         | 唤醒引脚 0                         |

| 17 | AVDD     | 3.3V 模拟电源输入                                                    | 49 | DAT1#           | 数字信号线                          |

| 18 | VREF     | 参考电压,100nF 滤波电容                                                | 50 | DAT2#           | 数字信号线                          |

| 19 | NC       |                                                                | 51 | DAT3#           | 数字信号线                          |

| 20 | VDD_I2   | 芯片供电,POWER_IN                                                  | 52 | VSSI03          | 数字地                            |

| 21 | DATO#    | 数字信号线                                                          | 53 | S0P2#           | 外接 100K 上拉电阻                   |

| 22 | VDDIO1_0 | 3.3V 输出,最大驱动电流<br>100mA(给 PIN17 的 AVDD<br>和 PIN46 的 VDDIO2 供电) | 54 |                 | Undefined                      |

| 23 | VDD2_0   | 1. 2V 输出,给 PIN1 的<br>VDD1 供电 | 55 | BAUD1 | 波特率配置端口1    |

|----|----------|------------------------------|----|-------|-------------|

| 24 | PLL_V12  | 外接滤波电容 0.1~1uF               | 56 | BAUD0 | 波特率配置端口0    |

| 25 | VSSI01   | 数字地                          | 57 | DAT4# | 数字信号线       |

| 26 | XTAL12MI | 12M 晶振输入                     | 58 |       | Undefined   |

| 27 | XTAL12MO | 12M 晶振输出                     | 59 | DAT5# | 数字信号线       |

| 28 | #RST     | 复位(低电平有效)                    | 60 | DAT6# | 数字信号线       |

| 29 | SOP1#    | 外接 100K 上拉电阻                 | 61 |       | Undefined   |

| 30 | NC       |                              | 62 | TEST  | 外接 10K 上拉电阻 |

| 31 | VDD_I1   | 芯片供电,POWER_IN                | 63 |       | Undefined   |

| 32 |          | Undefined                    | 64 | SVSS  | 数字地         |

#### 备注:

- 若只用到两个声道(pin8 和 pin9)中的一个声道,则另一个声道 pin 口必须悬空(不能接地,接地会导致电流大发热);

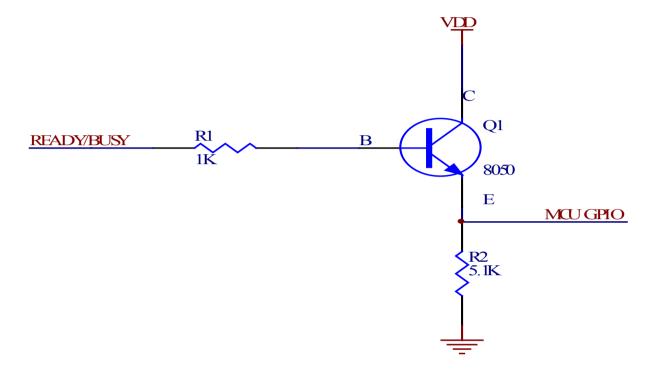

- 若应用过程中需查询硬件 Readby/Busy 口(pin40)的状态,则一定要将此 pin 口接上电默认为高阻抗输入状态的 PIN 口,若 MCU 无法实现,则需接外围电路辅助实现(参考电路见: 2.7 章 电压跟随器电路)

### 2 SYN6988 的参考电路

### 2.1 免责声明

画板完成后请仔细与我公司提供的参考电路进行比对,若用户未按照 我司提供的参考电路设计而造成的损失我司概不负责。如需对参考电 路进行优化设计,请将优化后的电路图提交我司核对。

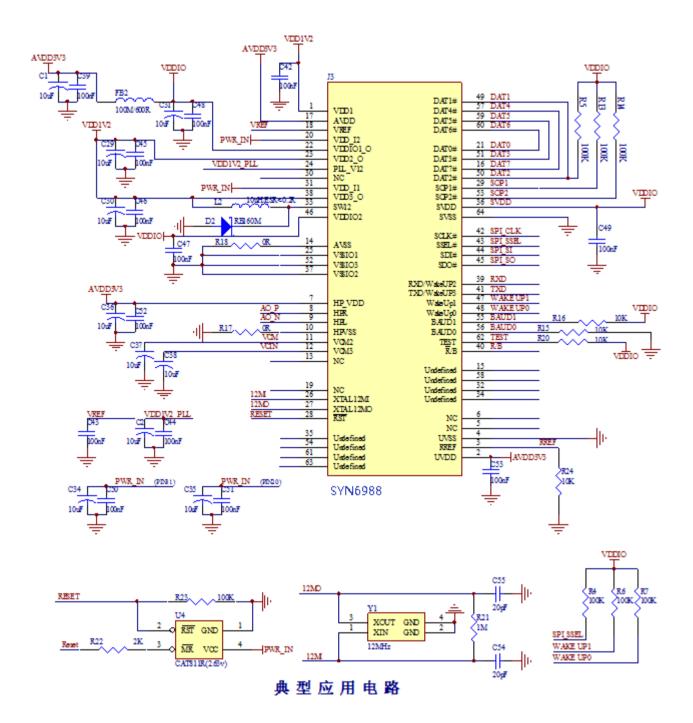

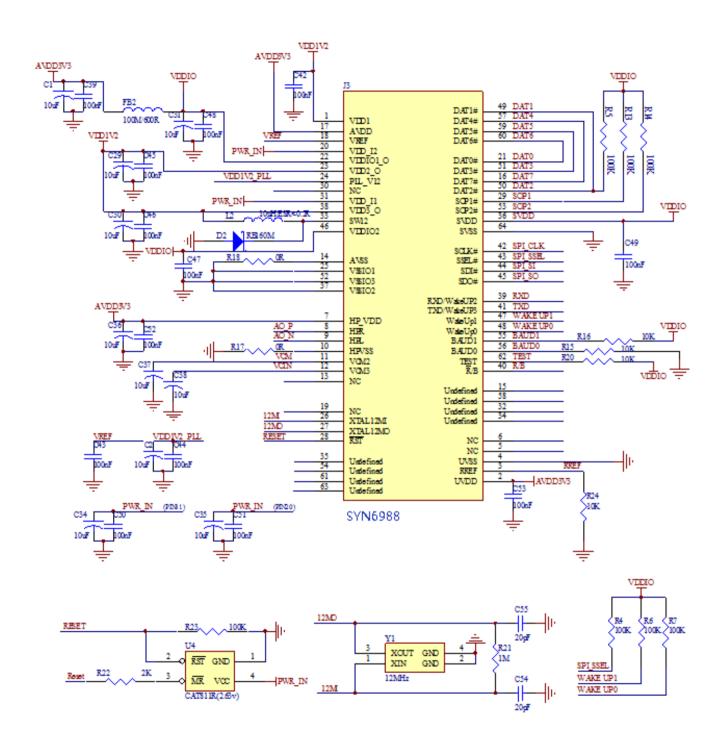

## 2.2 典型应用电路

### 2.3 复位方式

### 2.3.1 芯片复位外部条件

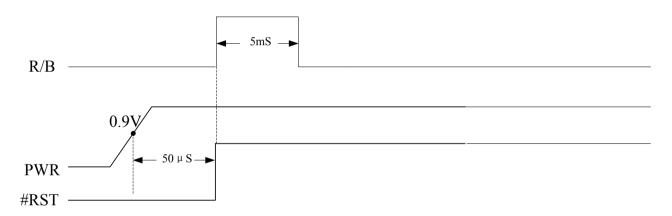

SYN6988 的 RST 是系统复位的控制管脚, 低电平有效。

- 1) 在系统电压上升到最小可工作电压之后,必须保证 RST 上至少有 50uS 的有效复位电平,也就是"上电请复位"。

- 2) 芯片的第 40 脚 R/B,为芯片状态输出脚,用来指示芯片是工作状态还是空闲状态,但是芯片在复位后的 5ms 内,此管脚是输入状态,若被外部强制拉低,芯片会进入自检流程,所以芯片复位时,必须保证 R/B 管脚至少有 5mS 的时间不被拉低。

- 3) **注意:** 50us 为最小复位时间,推荐 **20ms**; 5mS 为最小时间,可以更长。 R/B 管脚本身是带内部弱上拉的,所以外部可以悬空或不做处理,**只是不能被拉低**。

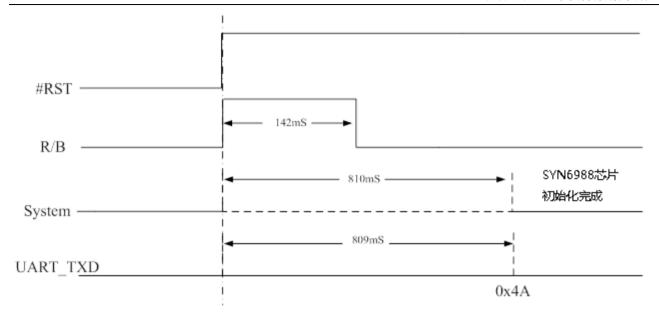

### 2.3.2 芯片初始化输出

- 1) 芯片复位后开始, R/B 管脚输出高电平,指示芯片处在 Busy 状态,142mS 后输出低电平,指示芯片处在 Ready 状态,但是此时芯片内部还没有初始化完成,用户不能此时发送命令控制芯片;

- 2) 芯片复位后开始,809ms 后 UART 口会返回 0x4A,表示系统真正初始化完成,此时用户可以发送命令控制芯片,如下图:

备注:上图参数可能会因为芯片的个体差异或者生产批次不同而略有不同,但是上图给出的参数是最大值。

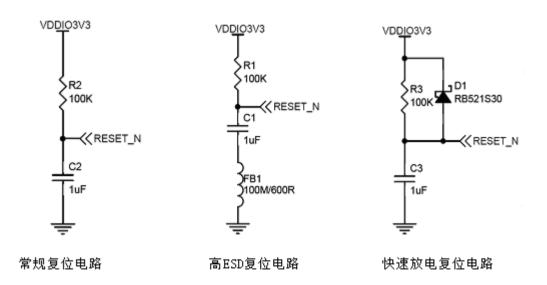

### 2.4 复位电路选择

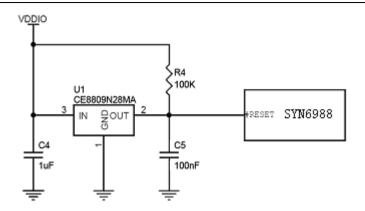

#### A) 可选择阻容复位电路,如下图

高 ESD 复位电路:在电容的接地处串接一个磁珠可以大大降低由 ESD 引起的系统重启概率,从而可以提高系统的 ESD 免疫能力。

**快速放电复位电路:** 在系统掉电时,RESET \_N 管脚的电平会很快的随着 VDDIO 的下降而下降。如果系统存在掉电之后又迅速上电或者电源浪涌比较大的情况,则建议使用此电路。

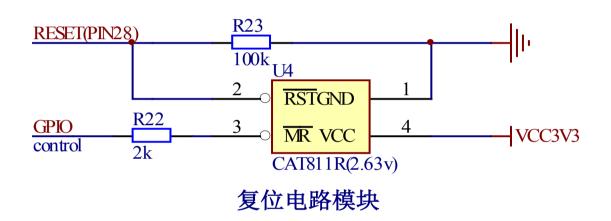

#### B) 选择专用IC复位芯片(推荐)

采用专用的复位IC 来实现MCU 的复位,复位时间长而精度高,稳定性好。图中的CE8808N28MA 是2.8V 检测电压的复位IC,可以提供长达200ms 的复位延时时间,如下如

专用复位IC的复位电路

PIN28 脚为 SYN6988 复位引脚 RESET

# 2.5 与上位机通讯连接

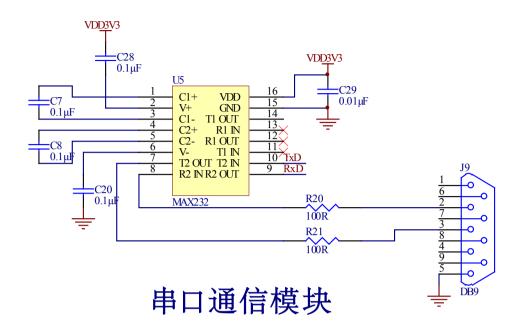

#### 2.5.1 UART 通讯

#### 波特率配置方法以及 R/B 的应用:

SYN6988 语音合成芯片的 UART 通信接口支持四种通信波特率: 4800bps、9600bps、57600bps、115200bps,可以通过芯片上的两个管脚 BAUD0 和 BAUD1 的电平来进行硬件配置,0: 表示低电平 1: 表示高电平

| 波特率       | BAUD0 | BAUD1 |

|-----------|-------|-------|

| 4800bps   | 0     | 0     |

| 9600bps   | 0     | 1     |

| 57600bps  | 1     | 0     |

| 115200bps | 1     | 1     |

芯片通过管脚 READY /BUSY (PIN40) 的电平来指示芯片的工作状态,芯片空闲状态时 READY /BUSY 管脚输出低电平,芯片在语音合成状态时 READY /BUSY 管脚输出高电平。

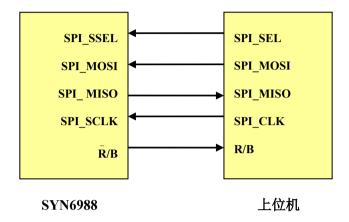

### 2.5.2SPI 通讯

# 2.6 音频功放电路

请参考《功放参考电路 V1.1. pdf》。

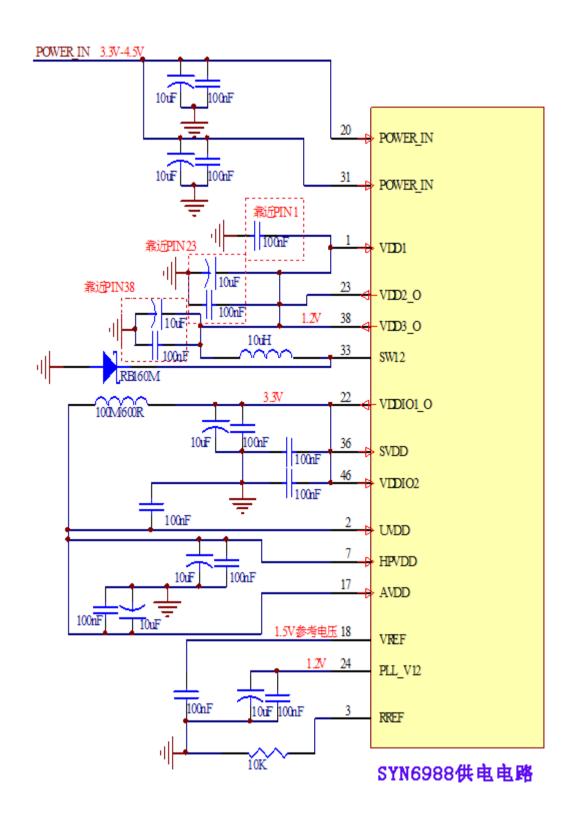

# 2.7 电源电路

#### 2.7.1 PowerIN

SYN6988 芯片集成了 LDO 和 DCDC 两组供电模块,非常稳定可靠,**VDD\_I1** (31 PIN) 为 DCDC 供电输入,**VDD I2** (20 PIN) 为 LDO 供电方式输入。

#### 2.7.2 VREF (PIN18)

VREF 是芯片内部产生的一个电压参考源,电压为 1.5V 。电源管理单元的所有电压输出都是以此电压作为基准。在硬件应用设计中只要**外挂一个滤波电容**即可。

#### 2.7.3 PLL V12 (PIN24)

LDO12\_PLL 是MCU 内部PLL 倍频电路的专用供电电源,一般不用作其他用途供电。在应用设计中只需要在其输出管脚处添加一个0.1~1uF 的滤波电容即可。Layout 时此滤波电容必须靠近芯片管脚摆放。

#### 2.7.4 VDD3 0 (PIN38)

DCDC 模块 1.2V 电压输出,与 VDD2\_0 (PIN23) 一起共同给内核 VDD1 (PIN1) 供电, Layout 时滤波电容 (C30、C46) 要尽量靠近芯片管脚。SW 开关信号走线要尽量短,并且要粗,VDD3\_0 (PIN38) 输出走线要远离 SW 开关信号。

RB160M 为续流二极管:原则上选取反向恢复时间小于 50ns 的肖特基二极管都可以,推荐 RB160M-40; 10uH 功率电感:选取 ESR 小于 0.2 欧姆的电感;

### 2.7.5 VDD2\_0 (PIN23)

LDO 部分 1.2V 电压输出,与 VDD3 0 (PIN38)一起共同给内核 VDD1 (PIN1)供电,

### 2.7.6 VDDIO1\_0 (PIN22)

3. 3V 输出, 最大驱动电流 100mA(给 PIN17 的 AVDD 和 PIN46 的 VDDI02 供电)

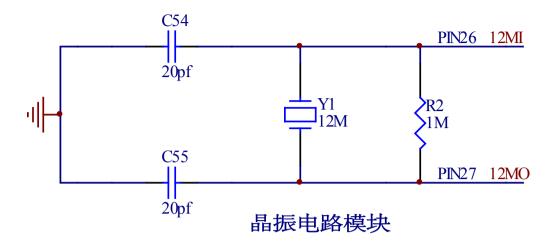

### 2.8 外接高速晶振

下图中的 R1 是反馈电阻,推荐使用 1M 欧姆。

下图中的电容 C54 和 C55 是时钟电路的谐振电容。推荐 C54 和 C55 使用 20pF。

#### ● 注意事项:

12MHz 晶振的频率误差不要大于±50ppm;

# 2.9 评估模块电路原理图

# 2.10 Readby/Busy 接口电压跟随器电路

说明:对 SYN6988 芯片,Readby/Busy端口在上电的瞬间不能被外部拉低(可以悬空或接高电平),否则芯片无法启动。若应用过程中需查询硬件 Readby/Busy口(pin40)的状态,则电路设计时必须把 SYN6988 的 PIN40 (R/B)端口接 MCU 的上电默认为高阻抗输入状态的 GPIO 口或是上电默认为高电平的接口或者是在上电初始化的第一时间把 MCU 的此 GPIO 配置为高阻抗输入状态、或输出高电平状态、或带上拉的输入状态,若 MCU 无法实现,则需接外围电路辅助实现,参考电路如下:

# 3 制板注意事项

### 3.1 晶振布局

晶振应尽量靠近 SYN6988 的 PIN26 (12MI) 和 PIN27 (12M0) 管脚放置, 遵循距离最短、走线宽、走线包地原则。同时, 晶振的谐振电容应紧靠其两侧。

### 3.2 电容布局

SYN6988 的各 PIN 口的对应滤波电容应尽量靠近其相应管脚。

### 3.3 音频线布线

SYN6988 的 AO\_P(PIN8) 和 AO\_N(PIN9), 要按差分走线的原则, 走线要宽、等长、并行、包地、远离晶

振及其他干扰源, 否则可能会带来杂音。

# 3.4 DCDC 电源电路

SW (PIN33) 开关信号走线要尽量短,并且要粗,Layout 时滤波电容(C30、C46) 要尽量靠近芯片管脚,VDD3 0(PIN38) 输出走线要远离 SW 开关信号。

# 4 SYN6988 产品规格

# 4.1 SYN6988 的封装数据图

| 标注 | 最小 (mm) | 最大 (mm) | 标注 | 最小 (mm) | 最大 (mm) |

|----|---------|---------|----|---------|---------|

| A  |         | 1.6     | D1 | 11.80   | 12. 20  |

| A1 | 0.05    | 0. 15   | е  | 0. 50   | (BSC)   |

| A2 | 1.35    | 1.45    | L  | 0.45    | 0.75    |

| b  | 0. 17   | 0.27    | θ  | 0°      | 7°      |

| С  | 0.09    | 0.20    | F  | 0.      | 08      |

| D  | 9.80    | 10. 20  |    |         |         |

SYN6988 外观形式和尺寸

# 4.2 电气特性

# 4.2.1极限参数

| 参数        | 符号                | 最小值  | 最大值  | 单位            |

|-----------|-------------------|------|------|---------------|

| 工作电压      | VDD_I1/VDD_<br>I2 | -0.3 | 4.5  | V             |

| 数字电源电压    | VDD1              | -0.3 | 1.32 | V             |

| 数字输入输出电压  | VDDI02            | -0.3 | 3.63 | V             |

| <b>数子</b> | SVDD              | -0.5 | 4.00 | V             |

|           | UVDD              | -0.3 | 3.63 | V             |

| 模拟电源电压    | AVDD              | -0.3 | 3.63 | V             |

|           | HPVDD             | -0.3 | 3.40 | V             |

| 最高工作温度范围  | То                | -40  | 85   | ${\mathbb C}$ |

| 存储温度      | Ts                | -55  | 125  | ${\mathbb C}$ |

# 4.2.2推荐电压工作范围

| 参数       | 符号            | 最小值   | 典型值   | 最大值  | 单位 |

|----------|---------------|-------|-------|------|----|

| 工作电压     | VDD_I1/VDD_I2 | 3. 1  | 3.6   | 4.5  | V  |

| 数字电源电压   | VDD1          | 1.08  | 1. 20 | 1.32 | V  |

| 数字输入输出电压 | VDDI02        | 2.97  | 3. 30 | 3.63 | V  |

|          | SVDD          | 3.00  | 3. 30 | 3.63 | V  |

|          | UVDD          | 3.00  | 3. 30 | 3.63 | V  |

| 模拟电源电压   | AVDD          | 3. 15 | 3. 30 | 3.63 | V  |

|          | HPVDD         | 3. 15 | 3. 30 | 3.63 | V  |

# 4.2.3音频 DAC 特性

| 参数        | 最小值  | 典型值  | 最大值 | 单位   |

|-----------|------|------|-----|------|

| 工作电压      | 3. 0 | 3. 3 | 3.6 | V    |

| HP最小负载电阻Ω |      | 32   |     | Ω    |

| 最大输出电压V   |      | 0.8  |     | Vrms |

| 最大输出功率    |      | 20   |     | mW   |

### 4.2.4DC 电气特性

| 参数        | 符号       | 最小值  | 典型值 | 最大值       | 单位   |

|-----------|----------|------|-----|-----------|------|

| 输入高电压     | VIH      | 2.0  | -   | VDDI0+0.3 | V    |

| 输入低电压     | VIL      | -0.3 | _   | 0.8       | V    |

| 输出高电压     | VOH      | 2. 4 | -   | -         | V    |

| 输出低电压     | VOL      | _    | _   | 0.4       | V    |

| 输入漏电流     | IL       | -    | -   | ±1        | uA   |

| 三态输出漏电流   | IOZ      | -    | -   | ±1        | uA   |

| 输入电容      | CI       | -    | -   | TBD       | pF   |

| 输出电容      | СО       | ı    | -   | TBD       | pF   |

| 立体声输出负载电阻 | Rlineout | 10   | _   | -         | Kohm |

| 耳机输出负载电阻  | RHP      | -    | 32  | _         | ohm  |

# 4.3 播放合成声音时的功耗

| 正常工    | 作状态下 | C+ 11   |

|--------|------|---------|

| 合成文本状态 | 空闲   | Standby |

| 53mA   | 15mA | 3mA     |